|

Как стать программистом Как устроен компьютер. Что такое программа. Как написать свою программу. И многое другое узнаете вы из этой книги. Получить бесплатно! |

Архитектура микроконтроллера

Микроконтроллеры / Для начинающих /Архитектура микроконтроллера - это, говоря простым языком, его внутреннее устройство. Можно сказать, что это некая структурная схема, которая содержит основные элементы, из которых состоит микроконтроллер.

Архитектура микроконтроллера позволяет понять, как устроен микроконтроллер конкретного семейства на уровне основных функциональных узлов. То есть архитектура описывает устройство микроконтроллера на уровне “железа”.

Если попробовать “завернуть” чуть более научно, то архитектура - это некий набор свойств, присущих семейству микроконтроллеров (микропроцессоров), или внутренняя организация этих устройств.

Имеются различные классификации архитектур по разным параметрам. Например, по количеству и скорости выполнения команд. Или по назначению (графические, математические, обработки сигналов и т.п.).

Кроме того, существует такое понятие, как архитектура команд микроконтроллера (микропроцессора). Это совместимость с определённым набором команд (например, с набором инструкций Intel x86), а также структура команд и способ выполнения команд.

Как вы понимаете, на сегодняшний день существует довольно много различных архитектур (как аппаратных, так и программных). Рассказать о всех в одной статье невозможно (да и не нужно). С учётом того, что практически все мои статьи и книги рассчитаны на начинающих, я буду пытаться рассказывать об архитектуре (и не только) как можно более простым и понятным языком (пусть даже иногда в ущерб точности и правильности).

Моя задача - объяснить сложные предметы далёким от темы людям, чтобы они хотя бы в общих чертах их поняли. Поэтому все дальнейшие материалы будут на примере одного из самых дешёвых и относительно простых микроконтроллеров ATtiny13A-SSU производства компании Atmel, который на момент написания этой статьи стоит всего 38 рублей (то есть примерно 0,7$). Этот микроконтроллер принадлежит к семейству AVR и имеет соответствующую архитектуру.

Я запланировал серию статей о микроконтроллерах для начинающих. Сразу скажу, что я не буду в этих статьях во всех подробностях рассказывать о программировании микроконтроллеров. Если кому интересно, то могу посоветовать отличный видеокурс по этой теме.

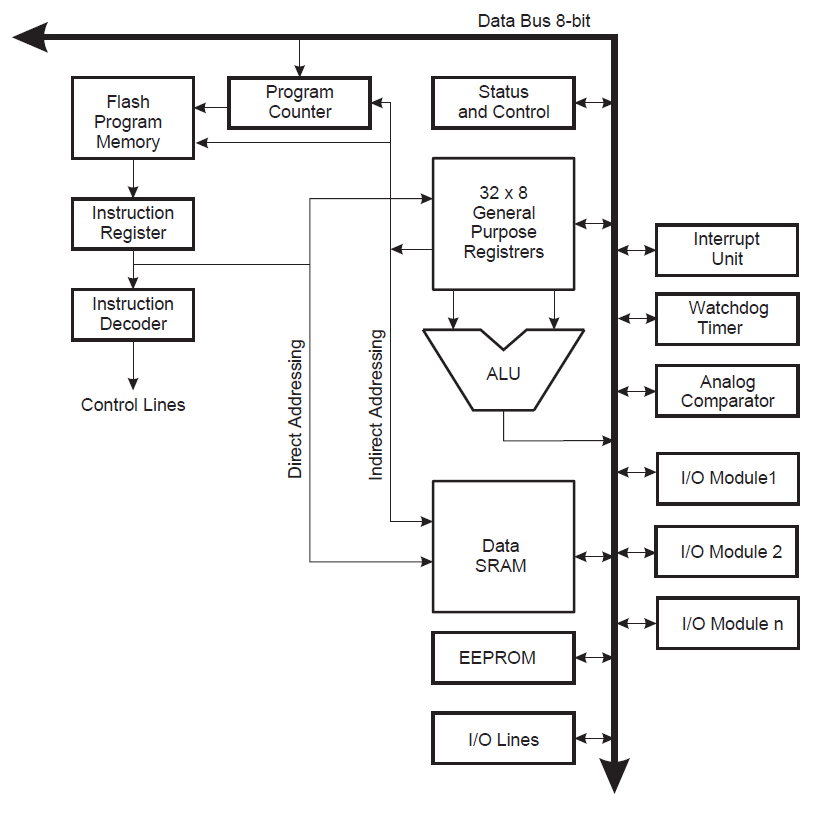

Ну а пока см. рисунок ниже, где показана архитектура ядра AVR в целом. То есть это относится ко всему семейству AVR, а не только к микроконтроллеру ATtiny13A.

Не пугайтесь непонятных слов и аббревиатур на английском языке, которые вы увидели на рисунке. Также не бойтесь, если что-то из того, что будет сказано далее, вам будет непонятно. В следующих статьях мы будем всё это подробно изучать. А пока самые общие сведения об архитектуре.

Ядро процессора

Основное назначение ядра процессора - это обеспечение правильного выполнения программы. Поэтому процессор должен быть в состоянии получать доступ к памяти, выполнять расчёты, управлять периферией и обрабатывать прерывания.

То, что вы видите на рисунке, это и есть ядро процессора.

Для достижения максимальной производительности и возможности параллельного выполнения команд AVR использует Гарвардскую архитектуру с раздельными памятью и шинами программ и данных.

Инструкции программы в памяти (блок Flash Program Memory, далее - FPM) выполняются с одноуровневой конвейеризацией. Пока одна инструкция выполняется, следующая инструкция программы предварительно считывается из памяти (из FPM). Эта концепция позволяет инструкции выполняться за один такт. Память программы (блок FPM) в системе - это перепрограммируемая флэш-память.

Блок регистров содержит 32 восьмиразрядных регистра общего назначения (далее - РОН) с быстрым доступом (на рисунке это 32 х 8 General Purpose Registrers). Доступ к регистру выполняется за один такт. Это позволяет арифметико-логическому устройству (АЛУ) - Arithmetic Logic Unit (ALU) также выполнять операции за один такт. В общем случае при выполнении операции АЛУ два операнда берутся из файлового регистра (Register File), выполняется операция, а результат записывается обратно в файловый регистр. И всё это за один такт.

Шесть из 32 регистров могут использоваться как 16-разрядные регистры косвенной адресации для указания на область адресов данных, обеспечивая эффективное вычисление адреса.

На рисунке это показано стрелкой с надписью Indirect address (косвенная адресация). То есть 6 из 32 регистров общего назначения можно использовать как указатели адреса для доступа к данным в области Data SRAM.

Один из этих указателей адреса можно также использовать как указатель адреса для просмотра таблиц в программной памяти (FPM). Эти дополнительные функциональные регистры, которые являются 16-разрядными регистрами X-, Y- и Z-, будут описаны далее.

АЛУ поддерживает арифметические и логические операции между регистрами или между константой и регистром. Операция с одним регистром также может быть выполнена в АЛУ. Операции с одним регистром также могут выполняться в ALU. После арифметической операции регистр состояния (Status Register) обновляется для отображения сведений о результате операции.

Выполнение программы обеспечивается условными и безусловными переходами и вызовами инструкций, способными непосредственно обращаться ко всему пространству адресов. Большинство инструкций AVR имеют формат одиночного 16-разрядного слова. Каждый адрес памяти программы содержит 16-или 32-разрядную инструкцию.

При генерации прерывания и вызове подпрограмм адрес возврата счетчика команд (Program Counter, сокращённо PC) сохраняется в стеке. Стек эффективно распределяется среди общих данных в SRAM, и, следовательно, размер стека ограничивается только общим размером SRAM и использованием SRAM. Все пользовательские программы должны инициализировать SP в подпрограмме сброса (перед выполнением подпрограмм или прерываний). Указатель стека (Stack Pointer, сокращённо SP) доступен для чтения и записи в пространстве ввода-вывода. К статическому ОЗУ данных (SRAM) можно легко получить доступ через пять различных режимов адресации архитектуры AVR.

Всё пространство памяти в архитектуре AVR является линейным и представляет собой обычные таблицы памяти.

Гибкий модуль прерываний содержит свои управляющие регистры в пространстве ввода-вывода (I/O space) с дополнительным битом глобального разрешения прерываний (Global Interrupt Enable) в регистре статуса (Status Register). Все прерывания имеют отдельный вектор прерываний (Interrupt Vector) в таблице векторов прерываний (Interrupt Vector table). Прерывания имеют приоритет в соответствии с их положением в таблице векторов прерываний. Чем ниже адрес вектора прерывания, тем выше приоритет.

Пространство памяти ввода-вывода содержит 64 адреса для периферийных функций центрального процессора (CPU) в качестве регистров управления (Control Registers), SPI и других функций ввода-вывода. Память ввода-вывода может быть доступна непосредственно, или как размещение пространства данных (Data Space), находящееся за регистром файла (Register File), 0x20 - 0x5F.

В следующих статьях я расскажу о некоторых частях ядра более подробно...

|

Вступить в группу "Основы программирования"

Подписаться на RUTUBE-канал Подписаться на Дзен-канал Подписаться на рассылки по программированию |

|

Микроконтроллеры для ЧАЙНИКОВ

Бесплатная рассылка о микроконтроллерах. Рассылка содержит как бесплатную информацию для начинающих, так и ссылки на платные продукты (книги, видеокурсы и др.) для тех, кто захочет вникнуть в тему более глубоко. Подробнее... |